Nexperia 74LVC(H)16373A-Q100 D-Typ-Transparent-Verriegelungen

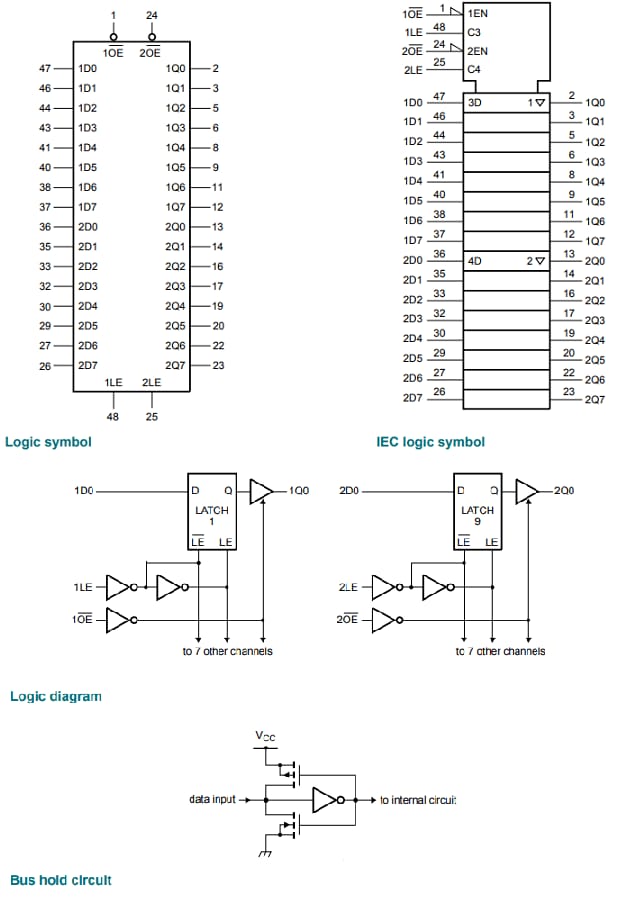

Nexperia 74LVC(H)16373A-Q100 16-Bit-D-Typ-Transparent-Verriegelungen verfügen über separate D-Typ-Eingänge mit Bus-Hold (nur 74LVCH16373A-Q100) für alle Verriegelungen und Dreistufenausgänge für Bus-orientierte Applikationen. Ein Sperrfreigabeeingang (LE) und eine Ausgangsfreigabe (OE) werden mit jeder achtfachen Verriegelung bereitgestellt. Die Eingänge können entweder von 3,3-V- oder 5-V-Bauteilen angesteuert werden, ermöglichen aber bei Deaktivierung ein Anlegen von 5,5 V an den Ausgängen. Diese Funktionen ermöglichen die Verwendung dieser Bauteile als Umsetzer in gemischten 3,3-V- und 5-V-Applikationen.Die 74LVC(H)16373A-Q100 16-Bit-D-Typ-Transparent-Verriegelungen enthalten die CMOS-Technologie mit geringem Stromverbrauch und eine Multibyte-Durchlauf-Standard-Pinbelegungsarchitektur. Diese Bauteile bestehen aus zwei Bereichen von acht D-Typ-Transparent-Verriegelungen mit echten Dreistufenausgängen. Wenn LE HIGH ist, treten Daten bei den Dn-Eingängen in die Verriegelungen ein. In diesem Zustand sind die Verriegelungen transparent, d. h. die Verriegelungsausgänge verändern jedes Mal ihre entsprechenden D-Eingangsänderungen.

Diese Produkte sind gemäß dem Automotive Electronics Council (AEC) Q100-Standard (Klasse 1) qualifiziert und eignen sich für den Einsatz in Fahrzeuganwendungen.

Merkmale

- Automotive-Produktqualifizierung gemäß AEC-Q100 (Klasse 1)

- Spezifiziert für einen Temperaturbereich von -40 °C bis +85 °C und von -40 °C bis +125 °C

- 5-V-tolerante Eingänge/Ausgänge für die Verbindung mit der 5-V-Logikschaltung

- Großer Spannungsversorgungsbereich von 1,2 V bis 3,6 V

- CMOS mit geringem Stromverbrauch

- Multibyte-Durchlauf-Standard-Pinbelegungsarchitektur

- Mehrere Versorgungspins mit geringer Induktivität für ein minimales Rauschen und reduzierte Erdungsprellen

- Direkte Schnittstelle mit TTL-Stufen

- Alle Dateneingänge verfügen über einen Bus-Hold (nur 74LVCH16373A-Q100)

- Hohe Induktivität, wenn VCC = 0 V

- Erfüllt JEDEC-Standard:

- JESD8-7A (1,65 V bis 1,95 V)

- JESD8-5A (2,3 V bis 2,7 V)

- JESD8-C/JESD36 (2,7 V bis 3,6 V)

- ESD-Schutz:

- MIL-STD-883, Methode 3015 übertrifft 2.000 V

- HBM JESD22-A114F übertrifft 2.000 V

- MM JESD22-A115-A übertrifft 200 V (C = 200 pF, R = 0 Ω)

- CDM ANSI/ESDA/JEDEC JS-002 übertrifft 1.000 V

Funktionsdiagramm

View Results ( 4 ) Page

| Teilnummer | Datenblatt | Zahl der Schaltkreise | Logiktyp | Logikfamilie | Anzahl der Ausgabezeilen | Oberer Ausgangsstrom | Unterer Ausgangsstrom | Verzögerungszeit Übertragungs | Versorgungsspannung - Min. | Versorgungsspannung - Max. | Anzahl der Kanäle | Anzahl der Eingabezeilen | Versorgungsstrom - Max. | Elemente pro Chip | Verpackung/Gehäuse |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 74LVC16373ADGV-Q1J |  |

2 Circuit | CMOS, TTL | LVC | 16 Line | - 24 mA | 24 mA | 6 ns | 1.2 V | 3.6 V | 2 Channel | 16 Input | 80 uA | TVSOP-48 | |

| 74LVCH16373ADGV-QJ |  |

2 Circuit | CMOS, TTL | LVCH | 16 Line | - 24 mA | 24 mA | 6 ns | 1.2 V | 3.6 V | 2 Channel | 16 Input | 80 uA | 2 Element | TVSOP-48 |

| 74LVC16373ADGG-Q1J |  |

LVC | TSSOP-48 | ||||||||||||

| 74LVCH16373ADGG-QJ |  |

2 Circuit | CMOS, TTL | LVCH | 16 Line | - 24 mA | 24 mA | 6 ns | 1.2 V | 3.6 V | 2 Channel | 16 Input | 80 uA | 2 Element | TSSOP-48 |

Veröffentlichungsdatum: 2019-05-29

| Aktualisiert: 2023-04-27